单板EMC设计之时钟布局优化(二)

单板EMC设计之时钟布局优化(二)

在一个电路系统中,时钟是必不可少的一部分。时钟电路相当关键,在电路中的作用犹如人的心脏一样,是使电路按照一定的时序有序工作、稳定运行的保障,但如果时钟电路设计的不合理,就会使时钟电路的强噪声耦合到输出线缆上导致RE辐射超标,因此在PCB中设计一个好的时钟电路是非常必要的。

一|晶振电路布局

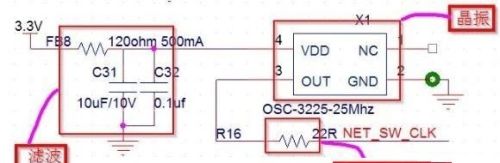

相比于晶体电路,晶振是有源电路,主要由三部分组成:晶振+电源滤波电路+源端匹配电阻,常见电路设计如下图:

对于电路中的参数,可以做一些调整,如FB8磁珠,可以换成220欧姆的或者更大的;如果晶振输出的时钟频率高于50MHz,滤波电容需加220pf去耦电容;图中的R16可以换成33欧姆或者更大,用以减缓时钟信号的上升沿。

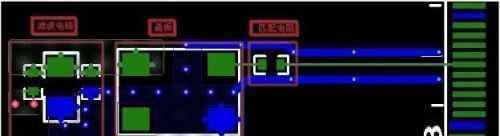

下图是晶振电路的布局走线示意图:

晶振电路布局、布线注意事项: (1)滤波电容靠近电源管脚,遵循先大后小原则摆放,小电容靠得最近;(2)匹配电阻靠近晶振摆放;如果原理图中没有这个电阻,可建议加上;(3)附近不要摆放大功率器件、如电源芯片、 MOS 管、电感等发热量大的器件;(4)时钟线按 50 欧姆阻抗线来走;如果时钟线过长,可以走在内层,打孔换层处加回流地孔;

(5)其他信号与时钟信号保持 4W 间距;

(6)包地处理,并加屏蔽地孔。

(7)时钟驱动电路及走线距离板边和出面板信号走线500mil以上。

二|时钟驱动器电路布局

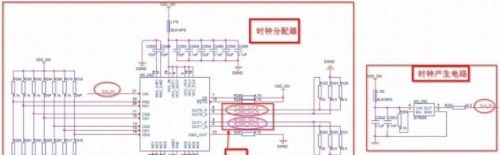

在大的单板设计中,由于芯片较多,所需的参考时钟较多,常用时钟驱动芯片来提供时钟。时钟驱动器包含三个部分:电源+时钟发生电路+时钟驱动器。具体如下图所示:

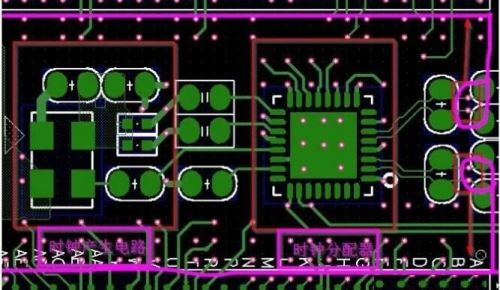

下图是时钟驱动电路的布局走线示意图:

晶振电路布局、布线注意事项:

(1)时钟发生电路要靠近时钟分配器,常见的时钟发生电路是晶体、晶振电路;(2)时钟分配电路放置在对称位置,保证到各个 IC 的时钟信号线路尽量短;(3)附近不要摆放大功率器件、如电源芯片、 MOS 管、电感等发热量大的器件;(4)时钟信号线过长时,最好走在内层,换层孔的 150mil 范围内要有回流地过孔;(5)时钟驱动电路及走线距离板边和出面板信号走线500mil以上。