cpu加法运算如何完成的(cpu加法器工作原理)

导语:老方法与新学科——CPU中加法是怎么做的

电脑玩家喜欢看CPU的主频,主频与计算速度到底是个啥关系呢?同一系列的CPU,主频越大,速度越快是没问题的。2G主频就是每一秒运行2X109个基本周期的意思。对不同的CPU来说,执行一个基本动作是要花费至少一个基本周期的。C语言中数加1可以用i++实现,机器指令汇编的形式可以写成:

Inc A

指的是内部寄存器A加1,如果Inc A是开机后第一条执行的机器指令,最少要花费两个基本周期,第一个周期是把指令从外部存储器取到CPU内部指令寄存器中,第二个周期是用算术逻辑运算器完成内部寄存器A上加1的运算。对现代CPU来说,取指令可以在CPU不向外部存储器写数据时,CPU存储管理器自己先取指令进入到内部缓存(catch)中,通常意义下执行到Inc A时,这个指令已经在cpu内部了,就不用再取了。也就是说一条指令只大致需要1个基本周期。

早期的CPU并行度可没那么高哦,速度也不快,一个做乘法的指令

Mul A,Addr

也许要花费几十个上百个基本周期的。即使是简单的加法,我记得CPU说明书上也会写要花费4-10个周期不等。早期为了让加法在尽量少的周期内做完,也是花费不少脑筋来研究的。下面我将类比CPU做加法与人做加法,简单说明计算机加法是如何做的,这些成果大致对应1955-1965年前后最优秀的计算机研究人员与设计师的工作,其实,用到的知识不超过现在高一学生的所学,优秀的小六学生至少可以领会50%。

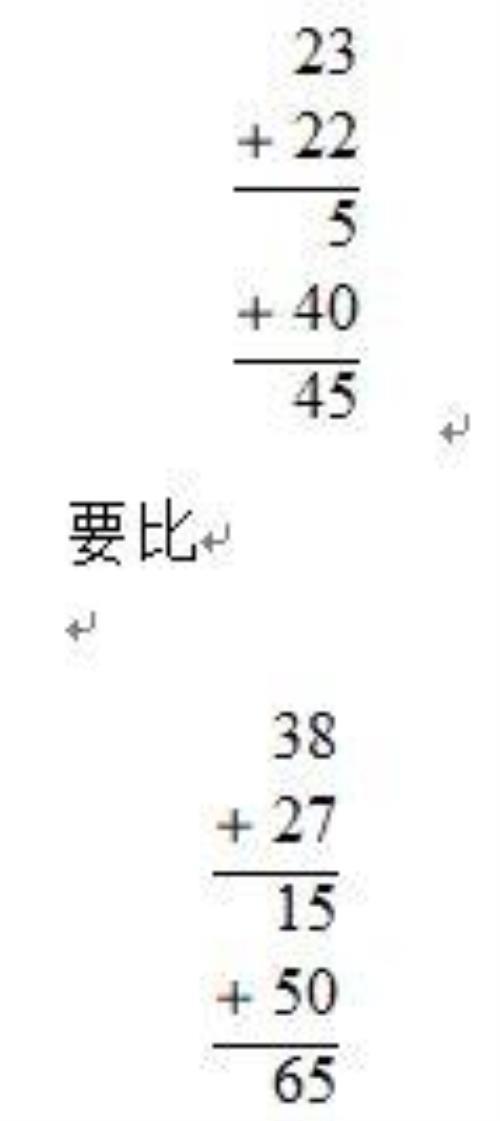

2. 加法与加法器人做加法的时候,规则是对位加,即个位与个位相加,十位与十位相加,百位与百位相加等等,且从低位开始到高位加。低年级小学生来觉得

简单。原因就是后者有进位。有进位的时候,除去要把当前位置的数加起来,还要再加上右边相邻位加出来的进位。这就是加法的全部规则。也就是说,只要知道个位数的加法方法,再有一个进位规则我们就可以做任意位数的加法了。这当然我们需要一个十进制个位数的加法表。

计算机算术逻辑运算器,是执行各种算术操作,逻辑操作的基本部件,加法器是其中完成加法的子部件,加法器设计面临的复杂性既与进制有关也与进位有关。

目前的计算机实际用电路上两条导线间的电压表示数,0近似为0v,1近似为2.5v,如果表示十进制数字就得十个不同的电压代表0,1,2,3,…….,8,9。电路功耗也比只要表示0,1,要增加几十到一百倍,如果初中同学知道电焦耳功率p=v^2/R是不难得出这个结论的。

计算机科学的先驱们,选择2进制做为计算机中数的基本进制。为了使得人能更好地与计算机交互,输入依然用10进制,内部将0,1,2,3,。。。。。,9用若干位二进制数编码。二进制编码的十进制数转换为实际的2进制数,再进行运算,输出结果还要转换成十进制数。不仅数字用二进制编码,所有的运算符号,甚至字母,汉字都是被二进制数编码的,这个编解码过程是用软件完成的。下面是一个2进制个位数的算表。

+ 0 1

0 0 1

1 0 10

进位的问题,十进制要看10进制加法表中粗分割线右下的部分。对9来说,就要看相邻低位是否有进位了,有进位都要加1,没进位就不用加。

运用基本的代数办法,将n位加n位的数如下图形式。

图1

如果学过数列,可以认为是四行数列,如果是小六学生,只需要想象0代表个位,1代表10位,等等也不难理解这个加法横式。A是被加数,B是加数,R是和,C就代表进位了。如果当前数位i产生了进位,Ci=1,否则Ci=0;框起来的部分就是一个完整的1位加法结构,输入变量有三个,分别是前面来的进位Ci-1,加数Ai,被加数Bi,输出有两个,第i位的和Ri以及第i位加产生的进位Ci。加法与加进位都按个位数算表来算,进位也可以根据个位数算表得到。为了规整,我们额外设了C0,只需简单认为是个0就可以了。而和的最高位Rn+1=Cn。换一种形式来表达这个第i位的加法结构,也叫1位加法器。

图2-1

图2-2

将n个这样相同1位加法器串联起来,就是一个n位加法器。现在的问题就成了怎么样做出1位加法器的问题。

3.一位加法器的实现图3-1 图3-2 图3-3

我们得先对只有0,1这样的数的算术做多点说明。第一是乘法, 二进制乘法比较好懂,算表如图3-1.第二是模2加法,模写成 mod,任意的自然数mod 5,就是被5除,其余数只能取0,1,2,3,4。任意的自然数mod 2的话,结果就只能是0,1。在下面的说明中如果特别指出来,“+”号都是指mod 2加。这样二进制个位数mod 2的加法表如图3-2所示。第三是反码,01010的反码是10101,个位取反码算符如图3-3。用代数举一个反码的例子,

用加法器的八个不同的输入值带入上面的公式中,按规则计算结果,输出是符合输出表值的。这就是加法器依据的最基本算式了。

下面的讲解就会粗一点,可能初中高中同学理解起来会有一点麻烦。我放弃严格性,尽可能说简单。图4-1是个叫MOS管的东西,可以在硅片制作出来。从电的性能上讲,就像一个可控电阻,G,S两端加上适合的电压D,S两端的电阻就会变得很小,很容易让电流流过,如果G,S之间电压接近0,D,S端电阻就会很大。

按图4-2接好电路后,注意在D端子上串联了一个电阻R,且加上了一个固定电压VSS。如果G,S端输入了一个接近于VSS的电压,让的D,S端电阻变小了(打开),电阻大大小于R的话,DS的输出电压就很小,接近于0。如果在G,S端的电压接近于0,D,S之间的通路呈现的电阻会大大大于R,这样DS端的电压就接近于VSS。也就是说这个电路实现了式(1),通常叫非门电路。而图5则用类似的办法实现了一个相乘再取反的运算,也叫做与非运算。图5,图4-2,只考虑逻辑关系的话,也可以用图6的逻辑符号表示。

利用 (1),(2),可以将(3)改写成:

这可以用两级与非门,外加几个非门实现。同理也可以实现Ci+1。具体的电路我就不画了。这里只讲讲原理。我这里的晶体管电路与实际的现代电路还是不一样的,从数学与结构的角度没错就是了。

4.n位加法器快速进位链至此,我们实现了任意长度的两个二进制数的加法了。但是这个电路过于低效了,原因就在进位上。

图7

考虑图7的加法,进位的情况,除去C0=0,每个Ci都为1,共计会产生n次进位,这样进位会传播经过好多个与非门电路,就会产生延迟。办法是用Ci的实际式子递归代替(4)中的右边的Ci,代数式子会变得复杂,但可以不用等待前一级电路算完,就可以算高位,并行确实使得速度加快了,但电路也随之复杂。这就是加法器设计要注意的问题了。光都会有传播时间,电路中电流的流动也是需要时间的。如果集成电路工艺使得晶体管变小了,那么传播距离变短,传播就快了。多个门串联造成的电信号延迟也随即减低,CPU基本周期就可以缩短。所以集成电路按28nm,14nm,10nm,7nm发生演化,这指的是集成电路中最窄图样的宽度。

希望高中程度较好的学生能抓住关键。其实这是大学计算机2年级课程的简化版,我们就是要尝试,将更多的新技术内容及早地传播给孩子们,让他们更早地进入创造阶段。

本文内容由快快网络小涵整理编辑!