计算机运算器工作过程与信号控制及芯片介绍(运算器的工作原理)

导语:计算机运算器工作过程与信号控制 及芯片介绍

1.运算器与控制器之间的信息传递

控制器中的程序计数器(PC)需要通过ALU完成指令地址计算,它把自己的内容送到ALU的A输入端,图3.4中用pc-in表示,以实现PC+4和PC+immed-2的加法运算,常数4和immed-2是由ALU的B输入端提供。PC+4的计算要在读取指令阶段完成,并在这一阶段就把计算结果(图中用pc-out表示)写回PC。PC+immed-2的计算要在指令译码阶段完成,并将计算结果保存在ALU的结果寄存器C中,到下一步的执行阶段依据需要把这个结果(图中用reg-C表示)再写回PC。

2.运算器与存储器器之间的信息传递

写入寄存器堆的数据可以是ALU的运算结果,也可能是从内存中读出来的数据,这二者需要通过一个二选一电路送到寄存器堆的DI数据输入端。ALU的计算结果是在执行阶段通过A op B或A op immed-1运算得到的,并首先保存在C寄存器中,到下一步的数据写回阶段才写入寄存器堆。

为了实现内存的读出或写入操作,在执行阶段通过A+immed-1运算得到内存地址,并保存在C寄存器中,到下一步的内存读写阶段用C中的这个地址来选择内存中的一个存储单元。

对从内存读出数据的指令,完成读出数据到内存的数据缓存寄存器DR中。对写数据到内存的指令,把在译码步骤保存在B寄存器中的数据送到内存的数据线,完成内存的写入操作。

小结:运算器需要向内存提供地址信息和写入的数据信息,内存则将向运算器提供其读出的数据以便写入到寄存器堆中。

请注意,这个运算器部件中的寄存器堆和ALU将在不同的执行步骤中完成自己的操作功能,读寄存器堆在前(需要提供被读的两个寄存器的编号rs和rt),ALU计算在后(需要提供数据来源选择信号A_sel和B_sel,以及ALU的运算功能选择信号alu_func),再到下一步才会把保存在寄存器C中的计算结果写回寄存器堆(需要提供被写的寄存器编号rd,写寄存器堆的命令信号we)。三个寄存器A、B、C都要用到时钟信号Clock。

芯片介绍Am2901

Am2901的内部组成

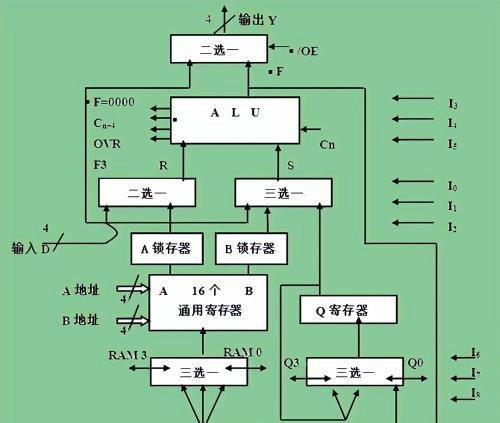

Am2901芯片是一个4位的位片结构的运算器器件,其内部组成框图如图3.5所示。

图3.5 Am2901 芯片的内部组成框图

该芯片的第一个组成部分是一个4位的算术逻辑运算部件ALU,它的输出为F,两路输入分别用R和S标记,还有送入ALU最低位的进位信号Cn,能实现R+S、S-R、R-S三种算术运算功能,和R∨S、R∧S、R∧S、R⊕S、R⊕S五种逻辑运算功能。在给出运算结果的同时,还送出向高位的进位输出信号Cn+4,溢出标志信号OVR,最高位的状态信号F3(可能用作符号位),以及运算结果为零的标志信号F=0000。

该芯片的第二个组成部分是由16个4位的通用寄存器组成的寄存器组。它是一个用双端口(A口和B口)控制读出,单端口(B口)控制写入的部件。为了对其进行读写,需通过A地址、B地址指定被读写的寄存器。两路读出数据分别用A口、B口标记,经锁存器线路可以送到ALU的R、S输入端的多路选择器,A口读出数据还可以用作该芯片的可选输出数据之一。寄存器组的写入数据由一组多路选择器给出,并由B地址选择写入的寄存器。

该芯片的第三个组部成分是一个4位的Q寄存器,主要用于实现硬件的乘法、除法指令,能对本身的内容完成左、右移位功能,能接收ALU的输出,输出送到ALU 的S 输入端。

该芯片的其余组成部分是5组多路数据选择器,每组都由4套电路组成,一套电路对应一个数据位,通过它们实现芯片内部的三个组成成分之间的连接,实现芯片内部与外部信息的输入输出操作,包括:经D输入接收外部送来的4位输入数据,经Y输出端输出4位数据到芯片外部。

请注意,在实现寄存器数据左、右移位操作时,会涉及到芯片内外部的数据交换,左移操作要求向运算器的最低位(图中用RAM0和Q0)送入移位输入数据,运算器的最高位(图中用RAM3和Q3)将向外部送出移位输出数据,右移操作要求向运算器的最高位送入移位输入数据,运算器的最低位将向外部送出移位输出数据。

(2) Am2901的控制与操作

控制信号包括:

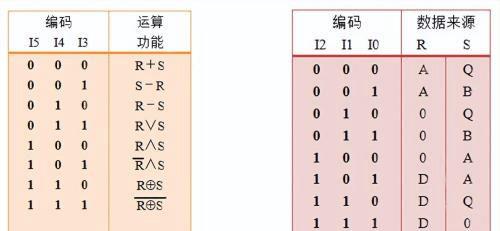

① 选择ALU的八种运算(三种算术运算、五种逻辑运算)功能中的一种。这可通过提供三位功能选择码I5,I4,I3实现,其具体规定列在表3.1中。

② 选择送入ALU的两个操作数据R和S的组合关系(数据来源)。图3.5上已标明,R从D和A中选择,S从A、B和Q中选择,再考虑到它们还均可选值,则我们选取最有用的8种组合,即A、Q组合,A、B组合,O、Q组合,0、B组合,0、A组合,D、A组合,D、Q组合,D、O组合,并用I2,I1,I0三位操作数选择码控制二组多路选通门选取其一,具体规定如表3.2所示。

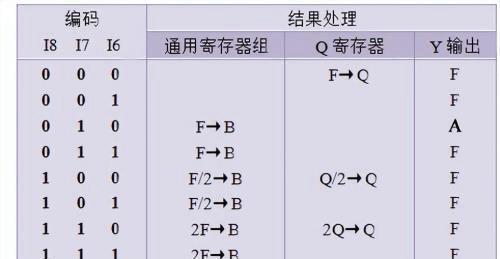

③ 选择运算结果或有关数据以什么方式送往何处的处理方案,这主要指通用寄存器组和Q寄存器执不执行接收操作或移位操作,以及向芯片的输出信息Y提供的是什么内容。这是通过I8,I7,I6三位结果选择码来控制三组相应的选择门实现的,其规定如表3.3所示。

表3.1 选择运算功能表 3.2数据来源选择

表3.3 选择结果处理方案

(3)外部的数据及线路 有一些数据是由在芯片之外的线路提供的,包括: ①芯片经D端接收的外部数据 ②芯片最低位的进位输入信号Cn ③关于左右移位操作过程中的RAM3、RAM0、Q3和Q0的输入数据 ④需要在芯片外设置接收与记忆4个标志位信息的电路

免责声明:本站部份内容由优秀作者和原创用户编辑投稿,本站仅提供存储服务,不拥有所有权,不承担法律责任。若涉嫌侵权/违法的,请反馈,一经查实立刻删除内容。本文内容由快快网络小岑创作整理编辑!