案例分析,NAND FLASH流水实现高速存储

流水技术原理

所谓流水线处理,如同生产装配线一样,是将操作执行工作量分成若干个时间上均衡的操作段,从流水线的起点连续地输入,流水线的各操作段以重叠方式执行。这使得操作执行速度只与流水线输入的速度有关,而与处理所需的时间无关。这样,在理想的流水操作状态下,其运行效率很高。

如果某个设计的处理流程分为若干步骤,而且整个数据处理是单流向的,即没有反馈或者迭代运算,前一个步骤的输出是下一个步骤的输入,则可以采用流水线设计方法来提高系统的工作效率。

利用流水线的设计方法,可大大提高系统的工作速度。这种方法可广泛运用于各种设计,特别是大型的、对速度要求较高的系统设计。虽然采用流水线会增大资源的使用,但是它可降低寄存器间的传播延时,保证系统维持高的系统时钟速度。在实际应用中,考虑到资源的使用和速度的要求,可以根据实际情况来选择流水线的级数以满足设计需要。

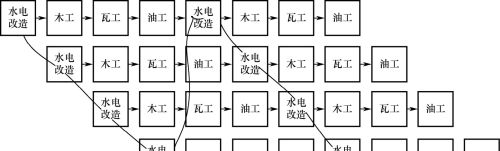

下面我们以房屋装修为例展示一下流水线的流程,如图3-7所示。

图3-7 房屋装修流水线示意图

房屋装修分4个步骤,分别是水电改造、木工上场、瓦工上场和油工上场。

如果设计团队由4个人员组成,那么在装修A小区某房屋的时候,需要按照上述出场顺序工作。水电改造工人完成A小区的工作后,可以去B小区某房屋工作,B小区工作完毕后,再去C小区工作。同理,木工、瓦工和油工也是如此。

我们可以得出结论,从水平方向上看,对于某个小区的房屋,需要四个人顺序出场;但是基于某个特定人员,在整个平面上来看,在平面方向上是排满饱和的。

所以基于团队,用流水线的方式确保了高效率,每个人工作量饱满,收益最大。

案例:NAND FLASH流水实现高速存储NAND FLASH的详细介绍见第9章。

我们知道,NAND FLASH的特点是读/写速度比较慢。

以写为例,写数据后,必须有长时间的编程等待时间,编程结束之后,才能进行下一次写数据过程。

例如:K9K4G08UOM这款芯片的最大写入时间(编程时间)为700 μs,写数据阶段的时间为125 μs(2 Kb/16 M,假如用16 MHz时钟,一次写入2 Kb个数据)。评估一下有效的写入速率为2 Kb/(125 μs+700 μs)=2.42 Mb/s。

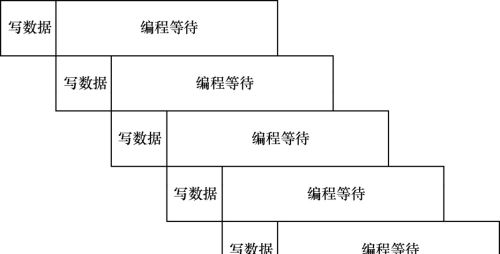

我们可以利用流水线技术来提高读/写速度,如图3-8所示。

图3-8 FLASH控制器流水线式进行写操作

示例中,我们用了5片芯片,为写入时间(编程时间)分配了800 μs的时间,为写数据分配了200 μs时间,组成了5级流水。第一片芯片写数据结束、编程等待的时候,对第二片芯片进行写数据,第二片芯片写数据结束、编程等待的时候,对第三片芯片进行写数据,以此类推,第五片芯片写数据结束后,重新对第一片芯片进行写数据。

重新评估一下写入速度为2Kb/200 μs=10Mb/s。

当然,上面的计算是为了方便读者理解来设定的,目的是让800 μs成为200 μs的整数倍,图片看上去美观一些。实际上我们还是用125 μs来进行写数据,写入速度接近16Mb/s。

在大容量存储类的项目中,不止使用流水线技术,还采用并行工作方式,优化之后的速度能达到几百兆。

以上介绍的为FLASH写阶段的流水线过程,读和擦除也可以利用流水线技术,此处不展开论述。

专栏推荐,【零基础学FPGA】本专栏基于Altera公司的器件和Verilog HDL语言。学完以后,相信读者能够掌握FPGA开发的基本技术,并能够独立进行FPGA项目开发。