神奇的ECC,可将内存的成本进一步降低

高端消费产品、网络和工业系统等内存密集型应用程序正面临着成本压力,这促使工程师寻找在提高性能的同时降低系统成本的新方法。错误码校正(ECC)是NAND闪存中维护可靠性和延长内存寿命的关键技术。为了在市场上实现基于NAND闪存的系统有更好的效率,与集成ECC的架构相比,开发人员更加倾向于在主机MCU中实现ECC架构。

本文将探讨集成的和基于主机的ECC之间的差异,比较一下每种方法对系统性能、可靠性和最终成本的影响。

ECC

简单说一下什么叫ECC。ECC内存即纠错内存,简单的说,其具有发现错误,纠正错误的功能,一般多应用在高档台式电脑/服务器及图形工作站上,这将使整个电脑系统在工作时更趋于安全稳定。

内存在其工作过程中难免会出现错误,而对于稳定性要求高的用户来说,内存错误可能会引起致命性问题。内存错误根据其原因还可分为硬错误和软错误。硬件错误是由于硬件的损害或缺陷造成的,因此数据总是不正确,此类错误是无法纠正的;软错误是随机出现的,例如在内存附近突然出现电子干扰等因素都可能造成内存软错误的发生。

当为一个系统选择闪存时,开发人员可以在NAND和NOR技术之间进行选择。NAND单元比NOR单元小,所以NAND的每位成本比NOR内存低。这反过来导致NAND闪存比NOR闪存可用的密度更高。此外,与NAND相比,NOR单元背后的物理原理导致了更长的程序擦除(P/E)时间。由于这些优点,NAND正以越来越快的速度被采用。

传统上NAND闪存的缺点是耐久性和读取性能较慢。随着时间的推移,NAND单元磨损或失去保持程序值的能力,将影响内存位转换状态。当一个块(Block)开始磨损时,它的数据可以转移到另一个块。随着单元的退化,为了防止数据丢失,我们便采用ECC技术。

ECC使用冗余来验证存储的数据是否与写入到内存的数据相匹配。此外,当检测到错误时,为了确保更高的数据完整性,ECC可以对每个块的错误数量进行修正。当超过某个错误阈值时,数据被移动到一个新块上。废弃的块被标记为“bad”,再也不会使用。因此,NAND闪存与ECC结合就可以提供高可靠性应用程序所需的完整性水平。

然而,由于ECC生成和检查需要时间过程,因此它会影响吞吐量和系统成本,这取决于它是如何实现的。通常,ECC可以与内存本身集成或由主机处理器在外部管理。集成方法有两种配置:

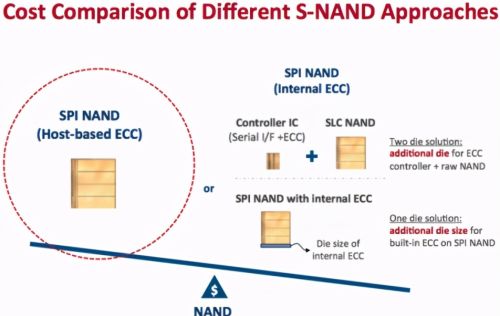

一种是单模方法,其中ECC是内存die的一部分,另一种是双模方法,其中控制器IC(具有串行接口和ECC)与内存die合并。在基于主机的方式下,ECC支持MCU NAND flash控制器去访问NAND。内存制造商提供的这三个选项允许OEM为他们的应用程序选择最佳的折衷方案。

一种灵活的ECC方法

将ECC集成到NAND闪存,具备了直接由存储器芯片本身管理ECC的优势。然而,尽管这种方法在某种程度上简化了系统设计,但代价是较高的内存成本和较低的读取性能。与主机处理器中使用的更高的内部时钟频率相比,闪存中较慢的内部时钟导致了读取性能的降低。

集成了ECC之后就增加了NAND闪存设备的大小和复杂性,因此内存成本会更高。考虑到一个8位ECC的硬件实现有大约50K。这表示对一个简单内存控制器的门数(gate count)(3000K)有~1.7%的影响。然而,如果集成在NAND存储器上,影响会在10-15%之间,并且会使存储器的成本增加更多。对于使用多内存设备的大内存需求系统,将ECC与NAND内存集成意味着要多次支付额外成本,而不是基于主机MCU一次性支付ECC。

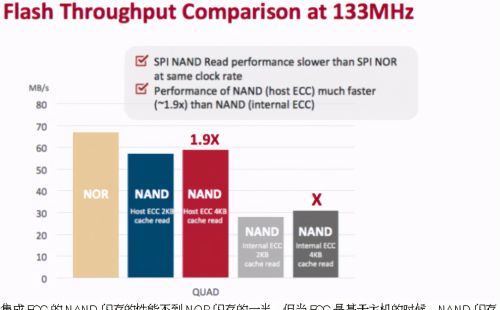

此外,读取性能也有所下降,因为集成ECC会增加延迟,每个内存读取的时钟率低于主机控制器可以处理ECC检查的时钟率。下图显示了NOR flash、集成ECC的NAND flash以及基于主机的ECC的NAND flash的读取吞吐量比较。可以看出,集成ECC的NAND闪存的性能不到NOR闪存的一半。然而,当ECC是基于主机的时候,NAND闪存的读取性能几乎翻倍,几乎与NOR闪存持平。

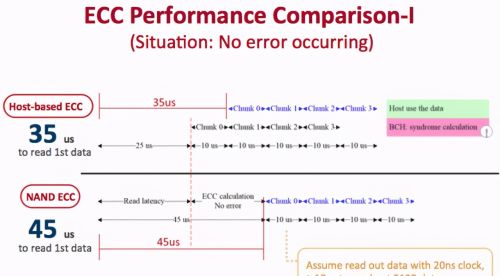

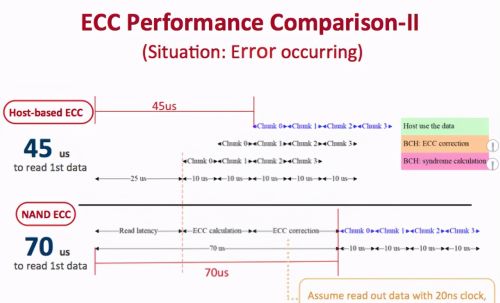

当检测到错误(并纠正错误)时,基于主机的ECC提供了更好的性能。下图显示了错误对读取第一数据时间(RFDT)的影响。通过集成ECC, RFDT从45微秒增加到70微秒。对于基于主机的ECC, RFDT要好得多,仅从35微秒增加到45微秒。